### **DESCRIPTION**

AMP Inc's storage devices are high capacity, solid-state, non-volatile Flash memory products, which comply with PC Card ATA and True IDE Mode industry standards.

AMP Inc's storage devices are compatible with virtually all of today's computing and communications systems. All AMP Inc's storage products support 3.3V and 5V operation, and 8, 16 and 32-bit technology. Most AMP Inc's storage products can be interchanged between systems, providing the broadest compatibility across platforms.

Flash data storage outperforms all other memory technologies for ruggedness, reliability, capacity, smaller size and low power consumption. The AMP Inc's COMFLASH Card's matchbook size and half-ounce weight make it the world's smallest removable data storage system. The amp inc's COMFLASH Card is ideal for a range of current and next-generation, small-form-factor consumer applications such as digital cameras, cellular phones, PDAs, personal communicators, pagers and audio recorders.

|                                                                                                                                                                             | AIVIP Part Number                                                                                                                                                                                    | Capacity |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| FEATURES                                                                                                                                                                    | AMPCF129M1S-vuxSNyC(I)-5C                                                                                                                                                                            | 128MB    |

| - Easy Installation                                                                                                                                                         | AMPCF257M1S-vuxSNyC(I)-5C                                                                                                                                                                            | 256MB    |

| <ul> <li>High Performance – up to 40 MB/sec host to buffer</li> </ul>                                                                                                       | AMPCF513M1S-vuxSNyC(I)-5C                                                                                                                                                                            | 512MB    |

| <ul> <li>ATA/IDE Interface – simple Plug and Play PC solution</li> </ul>                                                                                                    | AMPCF01DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 1GB      |

| - Extremely rugged and reliable                                                                                                                                             | AMPCF02DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 2GB      |

| - Low-power consumption                                                                                                                                                     | AMPCF04DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 4GB      |

| - Increased battery life over hard disk use                                                                                                                                 | AMPCF08DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 8GB      |

| - Built in "on the fly" ECC and wear leveling                                                                                                                               | AMPCF16DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 16GB     |

| - Support for CIS implemented with 256 bytes of attribute memory                                                                                                            | AMPCF32DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 32GB     |

| - Available in Industrial Temperature                                                                                                                                       | AMPCF64DG1S-vuxSNyC(I)-5C                                                                                                                                                                            | 64GB     |

| - Support- UDMA (up to UDMA-6), PCMCIA and IDE - S.M.A.R.T Capable - Compact Flash™ Specification version 4.1 Compliant - RoHS Compliant (Lead-Free)  Product Specification | V = Emulation Mode. (2 = mixed; 4 = removable; 6 = fixed) U = Operating Speed (0 = PIO; 7 = UDMA IDE; 8 = UDMA PCMCIA/IDE) X = Format option (F = Formatted; W = RAW) N = ROHS Compliant (Lead Free) |          |

|                                                                                                                                                                             | Y = Component density                                                                                                                                                                                |          |

|                                                                                                                                                                             |                                                                                                                                                                                                      |          |

I = Industrial Temp.

### **Operation description**

| Operating Voltage:        | Vcc Power                           | 3.3V ±10%;                                           |  |  |  |

|---------------------------|-------------------------------------|------------------------------------------------------|--|--|--|

| 1. Operating voitage:     | vcc Power                           | 5V±10%;                                              |  |  |  |

|                           |                                     | Read Mode: 20 mA (Max)                               |  |  |  |

|                           | 3.3V                                | Write Mode: 35 mA (Max)                              |  |  |  |

| 2. Typical Power          |                                     | Idle Mode: <<0.3mA                                   |  |  |  |

| Consumptions:             |                                     | Write Mode: 35 mA (Max)                              |  |  |  |

|                           | 5V                                  | Write Mode: 60 mA (Max)                              |  |  |  |

|                           |                                     | Standby Mode: <<1mA                                  |  |  |  |

|                           | Operating Temperature               | 0°C to +70°C (Standard), -40°C to +85°C (Industrial) |  |  |  |

|                           | Storage Temperature                 | -20°C to +85°C                                       |  |  |  |

| 3. Environment conditions | Relative Humidity                   | 5% ~ 95% (Max.)                                      |  |  |  |

| tions                     | Shock                               | 2000-G                                               |  |  |  |

|                           | Vibration                           | 15-G                                                 |  |  |  |

| 4. System Compatibility   | 0/S support DOS, Windows 98/ME/NT/2 | 2000/XP                                              |  |  |  |

### **Physical Description**

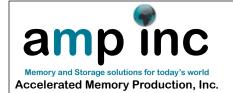

| 1.Weight and Measures | Type I              | Weight: 15 g       | LxWxH                                                            |  |

|-----------------------|---------------------|--------------------|------------------------------------------------------------------|--|

| (unit: m)             | (128MB- 64GB)       | Pin-Pitch: 1.27 mm | 36.4 x 42.8 x 3.3(mm)                                            |  |

| 2. Storage Capacities | Capacity            |                    | 128MB-64GB                                                       |  |

|                       |                     |                    | Read: up to 35MB/s                                               |  |

| 3. Performance        | Data Transfer Rates |                    | Write: up to 35MB/s                                              |  |

| 3. Performance        |                     |                    | Sustain Write 18MB/sec                                           |  |

|                       | Data Access Time    |                    | 1.2 ms                                                           |  |

|                       | MTBF                |                    | 4,000,000 hours*                                                 |  |

| 4 Poliobility         | Error Correction    |                    | Up to 24 random bits in 1024 bytes<br>Correction per second read |  |

| 4. Reliability        | ECC                 |                    | High reliability based on<br>Internal ECC function               |  |

|                       | Endurance           |                    | 2,000,000 Write/Erase cycles*                                    |  |

## **Pin Assignment**

| PC Card Memory Mode |          |                | PC  | Card I/O Mo | ode      | T   | rue IDE Mod | le       |

|---------------------|----------|----------------|-----|-------------|----------|-----|-------------|----------|

| No.                 | Pin Name | 1/0            | No. | Pin Name    | 1/0      | No. | Pin Name    | 1/0      |

| 1                   | GND      |                | 1   | GND         |          | 1   | GND         |          |

| 2                   | D03      | 1/0            | 2   | D03         | 1/0      | 2   | D03         | 1/0      |

| 3                   | D04      | 1/0            | 3   | D04         | 1/0      | 3   | D04         | 1/0      |

| 4                   | D05      | 1/0            | 4   | D05         | 1/0      | 4   | D05         | 1/0      |

| 5                   | D06      | 1/0            | 5   | D06         | 1/0      | 5   | D06         | 1/0      |

| 6                   | D07      | 1/0            | 6   | D07         | 1/0      | 6   | D07         | 1/0      |

| 7                   | #CE1     | 1              | 7   | #CE1        | 1        | 7   | #CE1        | 1,70     |

| 8                   | A10      | i              | 8   | A10         | i        | 8   | A10         | i        |

| 9                   | #0E      | i              | 9   | #OE         | ı        | 9   | #ATA SEL    | i        |

| 10                  | A09      | i              | 10  | A09         | i        | 10  | A09         | i        |

| 11                  | A09      | i              | 11  | A08         | <u>'</u> | 11  | A08         | <u> </u> |

|                     |          | <u>'</u>       |     |             | <u>'</u> |     |             | <u> </u> |

| 12                  | A07      | <del>  '</del> | 12  | A07         |          | 12  | A07         |          |

| 13                  | VCC      |                | 13  | VCC         |          | 13  | VCC         |          |

| 14                  | A06      | 1              | 14  | A06         | 1        | 14  | A06         | 1        |

| 15                  | A05      | 1              | 15  | A05         | 1        | 15  | A05         | 1        |

| 16                  | A04      | I              | 16  | A04         | 1        | 16  | A04         | I        |

| 17                  | A03      | I              | 17  | A03         | I        | 17  | A03         | I        |

| 18                  | A02      | I              | 18  | A02         | I        | 18  | A02         | 1        |

| 19                  | A01      | I              | 19  | A01         | I        | 19  | A01         | 1        |

| 20                  | A00      | I              | 20  | A00         | I        | 20  | A00         | I        |

| 21                  | D00      | I/O            | 21  | D00         | 1/0      | 21  | D00         | 1/0      |

| 22                  | D01      | 1/0            | 22  | D01         | 1/0      | 22  | D01         | 1/0      |

| 23                  | D02      | I/O            | 23  | D02         | 1/0      | 23  | D02         | 1/0      |

| 24                  | WP       | 0              | 24  | #I0IS16     | 0        | 24  | #I0CS16     | 0        |

| 25                  | #CD2     | 0              | 25  | #CD2        | 0        | 25  | #CD2        | 0        |

| 26                  | #CD1     | 0              | 26  | #CD1        | 0        | 26  | #CD1        | 0        |

| 27                  | D11      | 1/0            | 27  | D11         | 1/0      | 27  | D11         | 1/0      |

| 28                  | D12      | 1/0            | 28  | D12         | 1/0      | 28  | D12         | 1/0      |

| 29                  | D13      | 1/0            | 29  | D13         | 1/0      | 29  | D13         | 1/0      |

| 30                  | D14      | 1/0            | 30  | D14         | 1/0      | 30  | D14         | 1/0      |

| 31                  | D15      | 1/0            | 31  | D15         | 1/0      | 31  | D15         | 1/0      |

| 32                  | #CE2     | 1              | 32  | #CE2        | 1        | 32  | #CE2        | 1        |

| 33                  | #VS1     | 0              | 33  | #VS1        | 0        | 33  | #VS1        | 0        |

| 34                  | #IORD    | i              | 34  | #IORD       | ı        | 34  | #IORD       | ı        |

| 35                  | #IOWR    | i              | 35  | #IOWR       | i        | 35  | #IOWR       | i        |

| 36                  | #WE      | <u> </u>       | 36  | #WE         | i        | 36  | #WE         | l i      |

| 37                  | RDY/BSY  | 0              | 37  | IREQ        | 0        | 37  |             | 0        |

| 38                  | VCC      | 1 0            | 38  | VCC         | 0        | 38  | VCC         | -        |

|                     |          | 1 .            |     |             |          |     |             |          |

| 39                  | #CSEL    | 1              | 39  | #CSEL       | 1        | 39  | #CSEL       | 1        |

| 40                  | #VS2     | 0              | 40  | #VS2        | 0        | 40  | #VS2        | 0        |

| 41                  | RESET    | I              | 41  | RESET       | 1        | 41  | #RESET      | 1        |

| 42                  | #WAIT    | 0              | 42  | #WAIT       | 0        | 42  | IORDY       | 0        |

| 43                  | #INPACK  | 0              | 43  | #INPACK     | 0        | 43  | #INPACK     | 0        |

| 44                  | #REG     | 1              | 44  | #REG        | 1        | 44  | #REG        | 1        |

| 45                  | BVD2     | I/O            | 45  | #SPKR       | 1/0      | 45  | #DASP       | 1/0      |

| 46                  | BVD1     | 1/0            | 46  | #STSCHG     | 1/0      | 46  | #PDIAG      | 1/0      |

| 47                  | D08      | 1/0            | 47  | D08         | 1/0      | 47  | D08         | 1/0      |

| 48                  | D09      | I/O            | 48  | D09         | 1/0      | 48  | D09         | 1/0      |

| 49                  | D10      | I/O            | 49  | D10         | 1/0      | 49  | D10         | 1/0      |

| 50                  | GND      | 1/0            | 50  | GND         | 1/0      | 50  | GND         | 1/0      |

## **Signal Description**

| Signal Name                                                                  | I/O | Pin                            | Description                                                                                                                                                                                                                                                                |  |  |

|------------------------------------------------------------------------------|-----|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A0-A10<br>(PC Card Memory Mode)                                              |     | 8,10,11,12,                    | These address lines along with the #REG signal are used to select the I/O port address registers within the card, the memory mapped port address registers within the Card, a byte in the card's information structure and its configuration control and status registers. |  |  |

| A0-A10<br>(PC Card I/O Mode)                                                 | ı   | 14,15,16,17<br>18,19,20        | This signal is the same as the PC Card Memory Mode signal.                                                                                                                                                                                                                 |  |  |

| A0-A10<br>(True IDE Mode)                                                    |     |                                | In True IDE Mode only A0-A2 are used to select the one of eight registers in the ATA Task File, the others address lines should be grounded.                                                                                                                               |  |  |

| BVD1<br>(PC Card Memory Mode)                                                |     |                                | This signal is asserted high as the BVD1 signal since a battery is not used with this card.                                                                                                                                                                                |  |  |

| #STSCHG<br>(PC Card I/O Mode)                                                | I/O | 46                             | This signal is asserted low to alert the host to changes in the RDY/#BSY and Write Protect states, while the I/O interface is configured. The Card Configure and Status Register will control it.                                                                          |  |  |

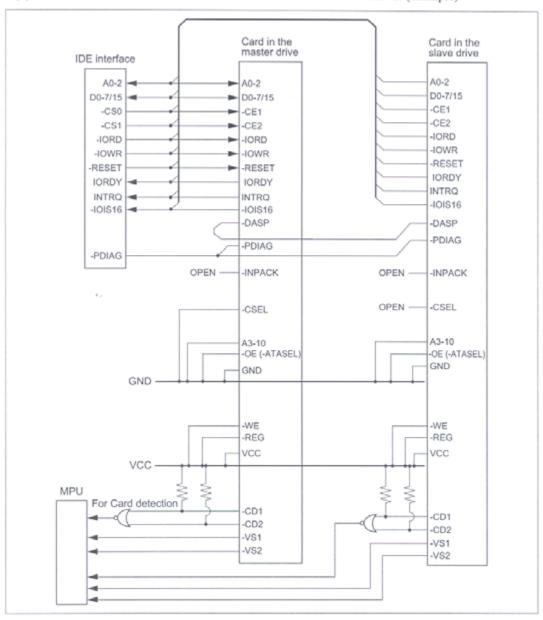

| #PDIAG<br>(True IDE Mode)                                                    |     |                                | In the True IDE Mode, this I/O is the Pass Diagnostic signal in the Master/Slave handshake protocol.                                                                                                                                                                       |  |  |

| BVD2<br>(PC Card Memory Mode)                                                |     |                                | This signal is always driven to a high state in Memory Mode since a battery is not required for this card.                                                                                                                                                                 |  |  |

| #SPKR<br>(PC Card I/O Mode)                                                  | 1/0 | 45                             | This signal is always driven to a high state in I/O Mode since this card does not support the audio function.                                                                                                                                                              |  |  |

| #DASP<br>(True IDE Mode)                                                     |     |                                | In the True IDE Mode, this I/O is the Disk Active/Slave Present signal in the Master/Slave handshake protocol.                                                                                                                                                             |  |  |

| #CD1, #CD2<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode) | 0   | 25, 26                         | These Card Detect pins are connected to ground on this card and u by the host to determine that the card is fully inserted into the socke                                                                                                                                  |  |  |

| #CE1, #CE2<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)                    | I   | 7,32                           | These signals are used both to select the card and to indicate to the card whether a byte or a word operation is being performed. #CE2 always accesses the odd byte of the word. #CE1 accesses the even byte or the odd byte of the word depending on A0 and #CE2.         |  |  |

| #CE1, #CE2<br>(True IDE Mode)                                                |     |                                | In the True IDE Mode, #CE1 is the chip select for the Task File Registers while #CE2 is used to select the Alternate Status and the Device Control Register.                                                                                                               |  |  |

| #CSEL<br>(PC Card Memory Mode)                                               |     |                                | This signal is not used for this mode.                                                                                                                                                                                                                                     |  |  |

| #CSEL<br>(PC Card I/O Mode)                                                  | ı   | 39                             | This signal is not used of this mode.                                                                                                                                                                                                                                      |  |  |

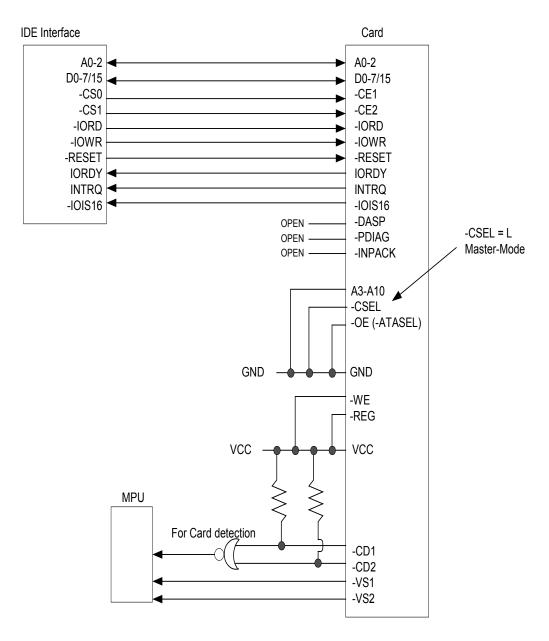

| #CSEL<br>(True IDE Mode)                                                     |     |                                | This internally pulled up signal is used to configure this card as a Master or a Slave. When this pin is grounded, this card is Master. When this pin is open, this card is Slave                                                                                          |  |  |

| D0-D15<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)                        | .,, | 2,3,4,5<br>6,21,22,23,         | These lines carry the Data, Commands and Status between the host and controller. D00 is the LSB of the even byte of the word. D08 is the LSB of the odd byte of the word.                                                                                                  |  |  |

| D0-D15<br>(True IDE Mode)                                                    | I/O | 27,28,29,<br>30,31,47,4<br>849 | In True IDE Mode, all Task File operations occur in the byte mode on the low order D00-D07 while all data transfers are 16 bits using D00-D15                                                                                                                              |  |  |

| GND<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)        |     | 1,50                           | Ground.                                                                                                                                                                                                                                                                    |  |  |

| #INPACK<br>(PC Card Memory Mode)  |          |    | This signal is not used in this mode.                                                                                                                              |

|-----------------------------------|----------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| , ,                               | $\dashv$ |    | The first Andrew Leden Street Constitution and the continuous street                                                                                               |

| #INPACK<br>(PC Card I/O Mode)     | 0        | 43 | The Input Acknowledge signal is asserted when the card is selected and responds to an I/O read cycle at the address on the address bus.                            |

| #INPACK                           |          |    |                                                                                                                                                                    |

| (True IDE Mode)                   |          |    | In the True IDE mode, this signal is not used.                                                                                                                     |

| #IORD<br>(PC Card Memory Mode)    | I        | 34 | This signal is not used in this mode.                                                                                                                              |

| #IORD<br>(PC Card I/O Mode)       |          |    | This is an I/O Read strobe generated by the host. This signal gates I/O data onto the bus from the card when the card is configured to used the I/O interface.     |

| #IORD<br>(True IDE Mode)          |          |    | In the True IDE mode, the signal is the same as the I/O Mode.                                                                                                      |

| #IOWR<br>(PC Card Memory Mode)    | 1        | 35 | This signal is not used in this mode                                                                                                                               |

| #IOWR<br>(PC Card I/O Mode)       |          |    | The I/O Write strobe is used to clock I/O data on the Data bus into the card controller registers when the card is configured to use the I/O interface.            |

| #IOWR<br>(True IDE Mode)          |          |    | In the True IDE Mode, this signal is the same as the I/O mode.                                                                                                     |

| #OE<br>(PC Card Memory Mode)      | ı        | 9  | This is an Output Enable Strobe generated by the host interface. It is used to read data from the card in Memory Mode and to read CIS and configuration registers. |

| #OE<br>(PC Card I/O Mode)         |          |    | In I/O Mode, this signal is used to read the CIS and configuration registers.                                                                                      |

| #ATA SEL<br>(True IDE Mode)       |          |    | To enable True IDE Mode, this signal should be grounded.                                                                                                           |

| RDY/#BSY<br>(PC Card Memory Mode) | 0        | 37 | In the Memory Mode, this signal is set high when card is ready to accept a new data transfer operation and held low when the card is busy.                         |

| #IREQ<br>(PC Card I/O Mode)       |          |    | I/O Operation. After the card has been configured for I/O Mode, this signal is used as Interrupt Request.                                                          |

| INTRQ<br>(True IDE Mode)          |          |    | In the True IDE Mode, this signal is the active high Interrupt Request to the host.                                                                                |

| #REG<br>(PC Card Memory Mode)     | I        | 44 | This signal is used during Memory Cycle to distinguish between Common Memory and Attribute Memory accesses. High for Common Memory and Low for Attribute Memory.   |

| #REG<br>(PC Card I/O Mode)        |          |    | This signal must be low during I/O Cycles when the I/O address is on the Bus.                                                                                      |

| #REG<br>(True IDE Mode)           |          |    | In the True IDE Mode, this signal is not used and should be connected to VCC by the host.                                                                          |

| RESET<br>(PC Card Memory Mode)                                               |   |        | When the signal is high, the signal Resets the card.                                                                                                      |  |  |  |

|------------------------------------------------------------------------------|---|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| RESET<br>(PC Card I/O Mode)                                                  | ı | 41     | When the signal is high, the signal Resets the card.                                                                                                      |  |  |  |

| #RESET<br>(True IDE Mode)                                                    |   |        | In the True IDE Mode, the signal is the active low hardware reset from the host.                                                                          |  |  |  |

| VCC<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode)        |   | 13, 38 | 5V, 3.3V                                                                                                                                                  |  |  |  |

| #VS1, #VS2<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)<br>(True IDE Mode) | 0 | 33, 40 | Voltage Sense Signals.                                                                                                                                    |  |  |  |

| #WAIT<br>(PC Card Memory Mode)<br>(PC Card I/O Mode)                         | 0 | 42     | This signal is driven low by the card to notify the host to delay completion of the memory of I/O cycle that is in progress.                              |  |  |  |

| IORDY<br>(True IDE Mode)                                                     |   |        | In the True IDE Mode, this signal may be used as IORDY.                                                                                                   |  |  |  |

| #WE<br>(PC Card Memory Mode)                                                 |   |        | This signal is driven by the host and used for generating memory write cycle to the registers of the card when the card is configured in the Memory Mode. |  |  |  |

| #WE<br>(PC Card I/O Mode)                                                    | 1 | 36     | In I/O mode, this signal is used for writing the configuration registers.                                                                                 |  |  |  |

| #WE<br>(True IDE Mode)                                                       |   |        | In the True IDE Mode, this signal is not used and should be connected to VCC by the host.                                                                 |  |  |  |

| WP<br>(PC Card Memory Mode)                                                  |   |        | Memory Mode, the card doesn't have a write protect switch. This signal is held low.                                                                       |  |  |  |

| #IOIS16<br>(PC Card I/O Mode)                                                | 0 | 24     | I/O Mode, A low signal indicates that a 16 bits or odd byte only operation can be performed by the addressed port.                                        |  |  |  |

| #IOIS16<br>(True IDE Mode)                                                   |   |        | In the True IDE Mode, this signal is asserted low when this device i expecting a word data transfer cycle.                                                |  |  |  |

## Overlapping I/O Mapping Addressing

Overlapping I/O Mapping (Primary, Secondary) Addressing

| #DEC | 410 | А       | 4-A9      |    |    |    |    | #IODD_"0"        | #1014/0-202     |  |

|------|-----|---------|-----------|----|----|----|----|------------------|-----------------|--|

| #REG | A10 | Primary | Secondary | A3 | A2 | A1 | A0 | #IORD="0"        | #IOWR="0"       |  |

| 0    | Х   | 1FH     | 17H       | 0  | 0  | 0  | 0  | Even read Data   | Even write Data |  |

| 0    | Х   | 1FH     | 17H       | 0  | 0  | 0  | 1  | Error            | Feature         |  |

| 0    | Х   | 1FH     | 17H       | 0  | 0  | 1  | 0  | Sector Count     | Sector Count    |  |

| 0    | Χ   | 1FH     | 17H       | 0  | 0  | 1  | 1  | Sector Number    | Sector Number   |  |

| 0    | Χ   | 1FH     | 17H       | 0  | 1  | 0  | 0  | Cylinder Low     | Cylinder Low    |  |

| 0    | Х   | 1FH     | 17H       | 0  | 1  | 0  | 0  | Cylinder High    | Cylinder High   |  |

| 0    | Χ   | 1FH     | 17H       | 0  | 1  | 1  | 0  | Drive/Head       | Drive/Head      |  |

| 0    | Χ   | 1FH     | 17H       | 0  | 1  | 1  | 1  | Status           | Command         |  |

| 0    | Х   | 3FH     | 37H       | 1  | 1  | 1  | 0  | Alternate Status | Device Control  |  |

| 0    | Х   | 3FH     | 37H       | 1  | 1  | 1  | 1  | Drive Address    | Reserved        |  |

## **True IDE Mode**

True IDE Mode

| #CSO | #CS1 | DA2 | DA1 | DA0 | #IORD="0"           | #IOWR="0"         |

|------|------|-----|-----|-----|---------------------|-------------------|

| 1    | 1    | Х   | х   | х   | Hi-Z                | Not Used          |

| 1    | 0    | 0   | х   | х   | Hi-Z                | Not Used          |

| 1    | 0    | 1   | 0   | х   | Hi-Z                | Not Used          |

| 0    | 0    | Х   | х   | Х   | Invalid             | Invalid           |

| 1    | 0    | 1   | 1   | 0   | Alternate<br>Status | Device<br>Control |

| 1    | 0    | 1   | 1   | 1   | Device Address      | Not Used          |

| 0    | 1    | 0   | 0   | 0   | Data                | Data              |

| 0    | 1    | 0   | 0   | 1   | Error               | Feature           |

| 0    | 1    | 0   | 1   | 0   | Sector Count        | Sector Count      |

| 0    | 1    | 0   | 1   | 1   | Sector<br>Number    | Sector<br>Number  |

| 0    | 1    | 1   | 0   | 0   | Cylinder Low        | Cylinder Low      |

| 0    | 1    | 1   | 0   | 1   | Cylinder High       | Cylinder High     |

| 0    | 1    | 1   | 1   | 0   | Drive/Head          | Drive/Head        |

| 0    | 1    | 1   | 1   | 1   | Status              | Command           |

### **Card Configuration Registers**

The table summarizes the drive four PCMCIA configuration registers. These read/write one-byte registers are located on even-byte attribute-plane addresses to ensure access in 8- and 16-bit system. Available card status information allows arbitration between resources that share interrupts and status of memory-only-card pins 16, 32, 62, and 63.

| Register           | Add. Off-<br>set <sup>1</sup> | R/W   | REG# | CE2# | CE1# | OE# | WE# | D15-8   | D7-0       |

|--------------------|-------------------------------|-------|------|------|------|-----|-----|---------|------------|

| Configuration      | 200h                          | Read  | L    | Н    | L    | Ы   | Н   | Invalid | Option     |

| Option             | 200h                          | Write | L    | Н    | L    | Н   | L   | Invalid | Option     |

| Card Configuration | 202h                          | Read  | L    | Н    | L    | L   | Н   | Invalid | Status     |

| And Status         | 20211                         | Write | L    | Н    | L    | Н   | L   | Invalid | Config.    |

| Dia Danis sament   | 2046                          | Read  | L    | Н    | L    | L   | Н   | Invalid | Pin Status |

| Pin Replacement    | Pin Replacement 204h          | Write | L    | Н    | L    | Н   | L   | Invalid | Pin Status |

| Cashet and Cash    |                               | Read  | L    | Н    | L    | L   | Н   | Invalid | Socket ID  |

| Socket and Copy    | 206h                          | Write | L    | Н    | L    | Н   | L   | Invalid | Socket ID  |

#### Notes

1 the host obtains attribute-memory address offset from the Configuration Tuple tpcc\_radr field when it reads the drive CIS.

### **Configuration Option Register**

The host uses the read/write Configuration Option register to configure the drive for drive for one of its four PCMCIA-ATA addressing modes, establish the interrupt signal mode, and issue a soft reset.

| 7    | 6      | 5 | 4 | 3            | 2        | 1 | 0 |

|------|--------|---|---|--------------|----------|---|---|

| SRST | IRQLv1 |   |   | Configuratio | on Index |   |   |

SRST Resets the card when 1. When 0 (default) after a hardware or software reset or power-on, the card is unconfigured.

A configuration occurs when a valid configuration index is written to bits 0-5.

**IRQLv1** Selects level mode interrupts when 1, pulse mode interrupts when 0 (default).

Conf IDX The host chooses an option from the card configuration table entry tuples and writes that option Configuration Index

number into this field. When zero (default), the memory-only interface is chosen, I/O accesses are disabled.

#### **Configuration & Status Register**

The Configuration and Status register contains card condition information.

| 7    | 6      | 5     | 4 | 3     | 2     | 1    | 0 |

|------|--------|-------|---|-------|-------|------|---|

| Chng | SigChg | lois8 | 0 | Audio | PwrDn | Intr | 0 |

**Chng** The Change bit indicates that a Pin Replacement register bit was changed.

SigChg The host sets/resets the Signal Changed bit to enable/disable a state-change signal from the status register. When set and the drive is configured for I/O, Chng controls pin 63 and is called the Changed Status signal. This bit should be 0 (BVD1/STSCHG# held high when

configured for I/O) if no state change signal is desired.

IOis8 Must be set if the host can only perform 8-bit I/O accesses.

Audio Audio is not supported

PwrDN Setting PwrDn places the drive in sleep mode. Host-initiated ATA task-file-register commands can also invoke low-power modes.

Intr This bit represents the interrupt request internal state. Its value is available whether or not interrupts are configured. It remains true

until the initiating-interrupt request is serviced.

### **Pin Replacement Register**

The Pin Replacement register provides card status information that is otherwise provided on memory-only interface pin 16, 33, 62, and 63. When written, bits 0-3 are masks for setting corresponding bits 4-7.

| CBvd | CBvd | Crdy/bsy# | CWP | RBvd | RBvd | Rrdy/bsy# | RWP |

|------|------|-----------|-----|------|------|-----------|-----|

| 7    | 6    | 5         | 4   | 3    | 2    | 1         | 0   |

**CBvd1, 2** Set when written, otherwise zero.

**Crdy/bsy#** Set when Rrdy/bsy# changes state or when written by the host.

CWP Zero unless set by the host. RBvd1, 2 Set unless cleared by the host.

Rrdy/bsy# Internal ready/busy# state when I/O mode uses RDY/BSY# pin for interrupt.

RWP Zero, since the flash drive has no write protect switch, unless set by the host.

#### **Socket and Copy Register**

The Socket and Copy register allows the drive to distinguish between similar drives at the same address. The flash drive does not support this feature.

| 7 | 6  | 5          | 4 | 3 | 2          | 1   | 0 |

|---|----|------------|---|---|------------|-----|---|

| 0 | Co | opy Number |   |   | Socket Num | ber |   |

Copy # The twin-card option is not supported

**Socket#** The socket number is ignored.

### **Task File Registers**

Data is transferred between the host and the card and the transfer controlled via the task file registers. The task file registers refer t the following series of registers.

- 1) Data register

- 2) Error register

- 3) Feature register

- 4) Sector count register

- 5) Sector number register

- 6) Cylinder low register

- 7) Cylinder High register

- 8) Drive head register

- 9) Status register

- 10) Alternate status register

- 11) Command register

- 12) Device control register

- 13) Drive address register

These registers are divided into five mapping modes (1) memory mapping, (2) primary I/O mapping, (3) secondary I/O mapping, (4) contiguous I/O mapping and (5) True-IDE mode I/O mapping, according to the address spaces to which these registers are assigned. The mapping mode is selected after the host writes a value in INDEX of the configuration optional register. Each mapping mode is explained below.

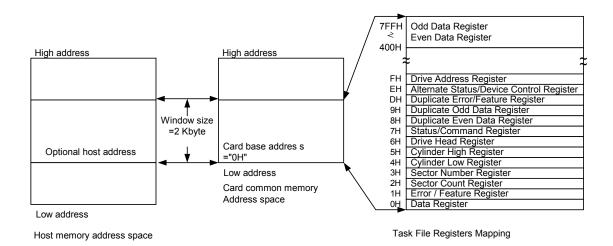

In the memory-mapping mode, the task file registers are assigned to the common memory area (see figure 3.3 below). As described in CIS (TPCE\_FA and TPCE\_MS of the configuration entry tuple), the memory window size is set at 2 Kbytes and the card base address at "0H". This window can be mapped to any address in the memory address space of the host. The position of the task file registers is determined by the offset address from the card base address. The 1-Kybte-memory window from offset "400H" to "7FFH" is secured for the host to access the data register during block transfer from memory to memory. Since this 1-Kbyte-memory window accesses F1FO, data cannot be accessed randomly.

Figure 3.3 Memory Mapping Mode

In the primary or secondary I/O mapping mode, the register functions as the I/O card to be accessed via "1F0H" to "1F7H" and "3F6H" to "3F7H" (primary) or "170H" to "177H" and "376H" to "377H" (secondary) in the standard I/O address space. Address signals of A9 to A0 are used for access and A10 neglected.

In the contiguous I/O mapping mode, only four address signals of A3 to A0 in the I/O address space are decoded. Thanks to this function, those other than A3 to A0 can be accessed via any address although host operation is required.

Table 3.3 shows task file registers mapping in the I/O card mode. The contiguous I/O mapping mode has the data and error/feature registers as well as the duplicate even data, duplicate odd data and duplicate error/feature registers. The data register can be accessed as 16-bit data combining 8-bit data indicated by an even address and 8-bit data indicated by an odd address. Since the data register overlaps the error/feature register when handled as 16-bit data, registers duplicating them are equipped.

Table 3.3 Memory and I/O Modes Decoding

| Primary I/O<br>Map<br>A9 to A0 | Secondary I/O<br>Map<br>A9 to A0 | Contiguous<br>Map<br>A3 to A0 | Task file register                       |

|--------------------------------|----------------------------------|-------------------------------|------------------------------------------|

| 1F0H                           | 170H                             | 0H                            | Data register                            |

| 1F1H                           | 171H                             | 1H                            | Error/feature register                   |

| 1F2H                           | 172H                             | 2H                            | Sector count register                    |

| 1F3H                           | 173H                             | 3H                            | Sector number register                   |

| 1F4H                           | 174H                             | 4H                            | Cylinder low register                    |

| 1F5H                           | 175H                             | 5H                            | Cylinder high register                   |

| 1F6H                           | 176H                             | 6H                            | Drive head register                      |

| 1F7H                           | 177H                             | 7H                            | Status/command register                  |

| -                              | -                                | 8H                            | Duplicate even data register             |

| -                              | -                                | 9H                            | Duplicate odd data register              |

| -                              | -                                | DH                            | Duplicate error/feature register         |

| 3F6H                           | 376H                             | EH                            | Alternate status/device control register |

| 3F7H                           | 377H                             | FH                            | Drive address register                   |

In the True-IDE mode I/O mapping mode, only three address signals of A2 to A0 in the I/O address space are decoded as shown in table 3.4, and the –CE2 signal is used to select the alternate status/ device control or drive address register and the –CE1 to select other task file registers.

Table 3.4 True-IDE Mode Decoding

| -CE2 | -CE1 | True-IDE Mode<br>I/O map A2 to A0 | Task file register                       |

|------|------|-----------------------------------|------------------------------------------|

| 1    | 0    | 0H                                | Data register                            |

| 1    | 0    | 1H                                | Error/feature register                   |

| 1    | 0    | 2H                                | Sector count register                    |

| 1    | 0    | 3H                                | Sector number register                   |

| 1    | 0    | 4H                                | Cylinder low register                    |

| 1    | 0    | 5H                                | Cylinder high register                   |

| 1    | 0    | 6H                                | Drive head register                      |

| 1    | 0    | 7H                                | Status/command register                  |

| 0    | 1    | 6H                                | Alternate status/device control register |

| 0    | 1    | 7H                                | Drive address register                   |

| Function         | ADDR           | R/W             | REG#  | CE2# | CE1# | OE# | WE# | IORD# | IOWR# | D15-8                | D7-0       |          |

|------------------|----------------|-----------------|-------|------|------|-----|-----|-------|-------|----------------------|------------|----------|

| No Operation     | X <sup>1</sup> |                 | Х     | Н    | н    | Х   | х   | Х     | х     | High-Z               | High-Z     |          |

|                  |                |                 | Н     | L    | L    | L   | Н   | Н     | Н     | Data High            | Data Low   |          |

| Data             | 000            | Read            | Н     | Н    | L    | L   | Н   | Н     | Н     | Invalid              | Data       |          |

| (see note 3)     | 000            | \A/-:-          | Н     | L    | L    | Н   | L   | Н     | Н     | Data High            | Data Low   |          |

|                  |                | Write           | Н     | Н    | L    | Н   | L   | Н     | Н     | Invalid              | Data       |          |

| F                |                | Danel           | Н     | Н    | L    | L   | Н   | Н     | Н     | Invalid              | Error      |          |

| Error            | 004            | Read            | Н     | L    | Н    | L   | Н   | Н     | Н     | Error                | Invalid    |          |

| 6.15             | 001            | 144.21          | Н     | Н    | L    | Н   | L   | Н     | Н     | Invalid              | Feature    |          |

| Set Feature      |                | Write           | Н     | L    | Н    | Н   | L   | Н     | Н     | Feature              | Invalid    |          |

| 6 1 6 1          | 000            | Read            | Н     | Х    | L    | L   | Н   | Н     | Н     | Invalid              | Sect. Cnt. |          |

| Sector Count     | 002            | Write           | Н     | Х    | L    | Н   | L   | Н     | Н     | Invalid              | Sect. Cnt. |          |

|                  |                |                 | Н     | Н    | L    | L   | Н   | Н     | Н     | Invalid              | Sect. No.  |          |

|                  |                | Read            | Н     | L    | Н    | L   | Н   | Н     | Н     | Sect. No.            | Invalid    |          |

| Sector Number    | 003            |                 | н     | Н    | L    | Н   | L   | Н     | Н     | Invalid              | Sect. No.  |          |

|                  |                | Write           | Н     | L    | н    | н   | L   | Н     | Н     | Sect. No.            | Invalid    |          |

|                  |                | Read            | Н     | Х    | L    | L   | н   | Н     | Н     | Invalid              | Cyl. Low   |          |

| Cylinder Low     | 004            | Write           | Н     | х    | L    | н   | L   | Н     | Н     | Invalid              | Cyl. Low   |          |

|                  |                |                 | Н     | н    | L    | L   | Н   | Н     | Н     | Invalid              | Cyl. High  |          |

|                  |                | Read            | Н     | L    | Н    | L   | Н   | Н     | Н     | Cyl. High            | Invalid    |          |

| Cylinder High    | 005            |                 | Н     | Н    | L    | Н   | L   | Н     | Н     | Invalid              | Cyl. High  |          |

|                  |                |                 | Write | Н    | L    | Н   | Н   | L     | Н     | Н                    | Cyl. High  | Invalid  |

| Drive/Head       | 006            | Read            | Н     | X    | L    | L   | Н   | Н     | Н     | Invalid              | Drv/Hd     |          |

| Jc/cud           |                | Write           | Н     | X    | L    | Н   | L   | н     | Н     | Invalid              | Drv/Hd     |          |

|                  |                | *******         | Н     | L    | L    | L   | Н   | Н     | Н     | Invalid              | Status     |          |

| Status           |                | Read            | Н     | Н    | Н    | L   | н   | н     | н     | Status               | Invalid    |          |

|                  | 007            |                 | Н     | L    | L    | Н   | L   | Н     | Н     | Invalid              | Command    |          |

| Command          |                | Write           | Н     | Н    | Н    | н   | L   | н     | н     | Command              | Invalid    |          |

|                  |                | Read            | Н     | L    | L    | L   | Н   | н     | н     | Data High            | Data Low   |          |

|                  |                | ricad           | Н     | Н    | L    | L   | н   | н     | н     | Invalid              | Data       |          |

|                  | 008            | 008             |       | Н    |      | L   | Н   | L     | Н     | н                    | Data High  | Data Low |

| Data             |                | Write           | Н Н   | Н    | L    | н   | L   | Н     | н     | Invalid              | Data       |          |

| (duplicate)      |                |                 | Н     | Н Н  | L    | L   | Н   | Н Н   | Н Н   | Invalid              | Data High  |          |

| (see note 3)     |                | Read            | Н Н   | L    | Н    | L   | н   | н     | н     |                      | Invalid    |          |

|                  | 009            |                 |       | Н    | L    |     | L   | Н     |       | Data High<br>Invalid |            |          |

|                  |                | Write           | Н     | L    | Н    | Н   | L   | Н     | Н     |                      | Data High  |          |

|                  | 004 000        |                 |       |      |      |     |     |       |       | Data High            | Invalid    |          |

| Invalid          | 00A – 00C      |                 | Н     | X    | X    | X   | Н   | X     | X     | Invalid              | Invalid    |          |

|                  |                | Read            | Н     | Н    | L    | L   | Н   | Н     | Н     | Invalid              | Error      |          |

| Error            | 00D            |                 | Н     | L    | Н    | L   | Н   | Н     | Н     | Error                | Invalid    |          |

| (duplicate)      |                | Write           | Н     | H    | L    | Н   | L   | Н     | Н     | Invalid              | Feature    |          |

|                  |                |                 | Н     | L    | Н    | Н   | L   | Н     | Н     | Feature              | Invalid    |          |

| Alternate Status | 00E            | Read            | Н     | Х    | L    | L   | Н   | Н     | Н     | Invalid              | Alt. Statu |          |

| Drive Control    |                | Write           | Н     | Х    | L    | Н   | L   | Н     | Н     | Invalid              | Control    |          |

|                  |                | Read            | Н     | Н    | L    | L   | Н   | Н     | Н     | Invalid              | Drv. Add.  |          |

| Drive Address    | 00F            |                 | Н     | L    | Н    | L   | Н   | Н     | Н     | Drv. Add             | Invalid    |          |

|                  |                | Write           | н     | Н    | L    | Н   | L   | Н     | Н     | Invalid              | Not Used   |          |

|                  |                | · · · · · · · · | Н     | L    | Н    | Н   | L   | Н     | Н     | Not Used             | Invalid    |          |

| Data (duplicate) | 400-7FF        | Read            | Н     | L    | L    | L   | Н   | Н     | Н     | Data High            | Data Low   |          |

| (see note 3)     | 400-711        | Write           | н     | L    | L    | н   | L   | н     | н     | Data High            | Data Low   |          |

- 1 X = don't care

- 2 The host must decode addresses All and above to provide card enables CE1# and CE2# that place the drive on a 2-K byte Boundary The drive decodes A0-10

- In independent memory mode, each byte access to 000, 008, or even addresses 400-7FE presents a new data buffer words on D0-15 Byte access to 009 or odd addresses 401-7FF present high byte buffer data on D0-7 or D8-15 depending on CDE1# and CE2#

#### I/O Mode Decoding

Starting with PCMCIA's PC Card standard 2.0, system I/O space can be used to access PC cards. The flash drive provides three I/O addressing modes:

- Independent I/O allows the drive to be mapped at any 16-byte I/O boundary. The host must decode I/O addresses A4 and above to provide cardenables CE1# and CE2#. The drive decodes addresses A0-3.

- Primary drive address at system ATA I/O address 1 F0h-1F7h and 3F6h-3F7. The host must decode I/O addresses A10 and above to provide cardenables CE1# and CE2#. The drive decodes addresses A0-9.

- Secondary drive address at system ATA I/O address 170h-177h and 376h-377. The host must decode addresses A10 and above to provide cardenables CE1# and CE2#. The drive decodes addresses A0-9. Independent I/O mode is the most flexible because it allows host to place the drive at any available 16-byte I/O address boundary. A system can use multiple flash drives, limited only by available 16-contiguous-byte I/O spaces.

- Primary and secondary drive addressing modes allow hosts to use the AT-standard's reserved disk drive I/O addressee. This provides PC system designers with the simplest way to accommodate ATA-protocol devices. Once the PCMCIA socket adapter is configured for the primary or secondary drive address ranges, a PC can take advantage of the BIOS's standard disk access routines.

- Additionally, since the PC's host adapter must decode addresses A10 and above within its 64-Kbyte I/O space, up to PCMCIA-ATA drivers can be placed at 4-kbyte boundaries. For example, drives can be placed at primary-type I/O addresses 01F0h, 11F0h, and 21F0h, ... F1F0h. Drives can also be placed at secondary-type I/O addresses 0170h, 1170h, 2170h, F1F0h

The following truth table shows PCMCIA-ATA I/O address modes.

## PCMCIA-ATA MODE-Independent I/O address = xx0-xxF<sup>2</sup>

| Function         | ADDR  | R/W                                    | REG#  | CE2# | CE1# | OE# | WE# | IORD# | IOWR# | D15-8      | D7-0       |         |        |

|------------------|-------|----------------------------------------|-------|------|------|-----|-----|-------|-------|------------|------------|---------|--------|

| No Operation     | X1    |                                        | Х     | Н    | Н    | Х   | Х   | Х     | Х     | High-Z     | High-Z     |         |        |

| no operation     |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Data Low   |         |        |

|                  |       | Read                                   | L     | L    | L    | н   | н   | L     | Н     | Data High  | Data Low   |         |        |

| Data             | 0     |                                        | L     | Н    | L    | н   | н   | Н     | L     | X          | Data Low   |         |        |

|                  |       | Write                                  | L     | L    | L    | Н   | Н   | Н     | L     | Data High  | Data Low   |         |        |

|                  |       |                                        | L     | H    | L    | Н   | Н   | L     | Н     | Invalid    | Error      |         |        |

| Error            |       | Read                                   | L     | L    | Н    | Н   | Н   | L     | Н     | Error      | Invalid    |         |        |

|                  | 1     |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Feature    |         |        |

| Set Feature      |       | Write                                  | L     | L    | Н    | Н   | Н   | Н     | L     | Feature    | Х          |         |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Sect. Cnt. |         |        |

|                  |       | Read                                   |       | L    | L    | Н   | Н   | L     | Н     | Sect. Cnt. | Sect. Cnt. |         |        |

| Sector Count     | 2     |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Sect. Cnt. |         |        |

|                  |       | Write                                  |       | L    | L    | Н   | Н   | Н     | L     | Sect. No.  | Sect. Cnt. |         |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Sect. No.  |         |        |

|                  |       | Read                                   | L     | L    | Н    | Н   | Н   | L     | Н     | Sect. No.  | Invalid    |         |        |

| Sector Number    | 3     | 3                                      | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Sect. No.  |         |        |

|                  |       | Write                                  | L     | L    | Н    | Н   | Н   | Н     | L     | Sect. No.  | Х          |         |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Cyl. Low   |         |        |

|                  |       | Read                                   |       | L    | L    | Н   | Н   | L     | Н     | Cyl. High  | Cyl. Low   |         |        |

| Cylinder Low     | 4     |                                        | L     | Х    | L    | Н   | Н   | Н     | L     | X          | Cyl. Low   |         |        |

|                  |       | Write                                  |       | Х    | L    | Н   | Н   | Н     | L     | Cyl. High  | Cyl. Low   |         |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Cyl. High  |         |        |

|                  | 5 —   | _                                      | Read  | L    | L    | Н   | Н   | Н     | L     | Н          | Cyl. High  | Invalid |        |

| Cylinder High    |       |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | X          | Cyl. High  |         |        |

|                  |       |                                        | Write | L    | L    | Н   | Н   | Н     | Н     | L          | Cyl. High  | X       |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Drv/Hd     |         |        |

|                  |       | Read                                   |       | L    | L    | Н   | Н   | L     | Н     | Status     | Drv/Hd     |         |        |

| Drive/Head       | 6     |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Drv/Hd     |         |        |

|                  |       | Write                                  |       | L    | L    | Н   | Н   | Н     | L     | Command    | Drv/Hd     |         |        |

|                  |       |                                        |       |      | L    | Н   | L   | Н     | Н     | L          | Н          | Invalid | Status |

| Status           |       | Read                                   | L     | L    | Н    | Н   | Н   | L     | Н     | Status     | Invalid    |         |        |

|                  | 7     |                                        | L     | н    | L    | Н   | Н   | Н     | L     | х          | Command    |         |        |

| Command          |       | Write                                  | L     | L    | Н    | Н   | Н   | Н     | L     | Command    | Х          |         |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Data Low   |         |        |

|                  | _     | Read                                   | L     | L    | L    | Н   | Н   | L     | Н     | Data High  | Data Low   |         |        |

|                  | 8     |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | х          | Data Low   |         |        |

| Data             |       | Write                                  |       | L    | L    | Н   | Н   | Н     | L     | Data High  | Data Low   |         |        |

| (duplicate)      |       | l                                      | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Data High  |         |        |

|                  | _     | Read                                   | L     | L    | Н    | Н   | Н   | L     | Н     | Data High  | Invalid    |         |        |

|                  | 9     |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Data High  |         |        |

|                  |       | Write                                  | L     | L    | Н    | Н   | Н   | Н     | L     | Data High  | Х          |         |        |

| Invalid          | A – C |                                        | L     | Х    | Х    | Х   | Х   | Х     | Х     | Invalid    | Invalid    |         |        |

|                  |       |                                        | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Error      |         |        |

| Error            |       | Read                                   | L     | L    | Н    | Н   | Н   | L     | Н     | Error      | Invalid    |         |        |

| (duplicate)      | D     |                                        | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Feature    |         |        |

|                  |       | Write                                  | L     | L    | Н    | Н   | Н   | Н     | L     | Feature    | Х          |         |        |

| Alta-mark Civi   |       | D                                      | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Alt Status |         |        |

| Alternate Status | E     | Read                                   | L     | L    | L    | Н   | Н   | L     | Н     | Drv. Add   | Alt Status |         |        |

| 5                |       | 144 **                                 | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Control    |         |        |

| Drive Control    |       | Write                                  | L     | L    | L    | Н   | Н   | Н     | L     | Not Used   | Control    |         |        |

|                  |       | De - d                                 | L     | Н    | L    | н   | Н   | L     | Н     | Invalid    | Drv. Add   |         |        |

| Drive Address    | F     | Read                                   | L     | L    | Н    | Н   | Н   | L     | Н     | Driv. Add  | Invalid    |         |        |

| Drive Address    | г     | Write                                  | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Not Used   |         |        |

|                  |       | ************************************** | L     | L    | Н    | Н   | Н   | Н     | L     | Not used   | Х          |         |        |

## PCMCIA-ATA MODE-Primary address = 1F0-1F7, 3F6-3F7; Secondary address = 170-177, 376-377<sup>3</sup>

| Function         | ADDR           | R/W      | REG#  | CE2# | CE1# | OE# | WE# | IORD# | IOWR# | D15-8      | D7-0       |           |

|------------------|----------------|----------|-------|------|------|-----|-----|-------|-------|------------|------------|-----------|

| No Operation     | X <sup>1</sup> |          | Х     | Н    | Н    | Х   | Х   | Х     | Х     | High-Z     | High-Z     |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Data Low   |           |

| D-4-             | 0              | Read     | L     | L    | L    | Н   | Н   | L     | Н     | Data High  | Data Low   |           |

| Data             | U              | NA/wik - | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Data Low   |           |

|                  |                | Write    | L     | L    | L    | Н   | Н   | Н     | L     | Data High  | Data Low   |           |

| F                |                | Deed     | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Error      |           |

| Error            |                | Read     | L     | L    | Н    | Н   | Н   | L     | Н     | Error      | Invalid    |           |

| Cat Fasting      | 1              | NA/wik - | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Feature    |           |

| Set Feature      |                | Write    | L     | L    | Н    | Н   | Н   | Н     | L     | Feature    | Х          |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Sect. Cnt. |           |

|                  |                | Read     | L     | L    | L    | Н   | Н   | L     | Н     | Sect. Cnt. | Sect. Cnt. |           |

| Sector Count     | 2              |          | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Sect. Cnt. |           |

|                  |                | Write    | L     | L    | L    | Н   | Н   | Н     | L     | Sect. No.  | Sect. Cnt. |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Sect. No.  |           |

|                  |                | Read     | L     | L    | Н    | Н   | Н   | L     | Н     | Sect. No.  | Invalid    |           |

| Sector Number    | 3              |          | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Sect. No.  |           |

|                  |                |          | Write | L    | L    | Н   | Н   | Н     | Н     | L          | Sect. No.  | Х         |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Cyl. Low   |           |

|                  | 4              | Read     | L     | L    | L    | Н   | Н   | L     | Н     | Cyl. High  | Cyl. Low   |           |

| Cylinder Low     |                |          | L     | х    | L    | Н   | Н   | Н     | L     | Х          | Cyl. Low   |           |

|                  |                | Write    | L     | х    | L    | Н   | Н   | Н     | L     | Cyl. High  | Cyl. Low   |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Cyl. High  |           |

|                  | 5              | Read     | L     | L    | Н    | Н   | Н   | L     | Н     | Cyl. High  | Invalid    |           |

| Cylinder High    |                |          |       | L    | Н    | L   | Н   | Н     | Н     | L          | Х          | Cyl. High |

|                  |                | Write    | L     | L    | Н    | Н   | Н   | Н     | L     | Cyl. High  | Х          |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Drv/Hd     |           |

|                  | _              | Read     | L     | L    | L    | Н   | Н   | L     | Н     | Status     | Drv/Hd     |           |

| Drive/Head       | 6              |          | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Drv/Hd     |           |

|                  |                | Write    |       | L    | L    | Н   | Н   | Н     | L     | Command    | Drv/Hd     |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Status     |           |

| Status           |                | Read     | L     | L    | Н    | Н   | Н   | L     | Н     | Status     | Invalid    |           |

|                  | 7              |          | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Command    |           |

| Command          |                | Write    | L     | L    | Н    | н   | Н   | Н     | L     | Command    | Х          |           |

| Invalid          | A – C          |          | L     | х    | х    | х   | Х   | Х     | Х     | Invalid    | Invalid    |           |

|                  | _              |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Alt Status |           |

| Alternate Status | E              | Read     | L     | L    | L    | Н   | Н   | L     | Н     | Drv. Add   | Alt Status |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Control    |           |

| Drive Control    |                | Write    | L     | L    | L    | Н   | Н   | Н     | L     | Not Used   | Control    |           |

|                  |                |          | L     | Н    | L    | Н   | Н   | L     | Н     | Invalid    | Drv. Add   |           |

|                  |                | Read     | L     | L    | Н    | Н   | Н   | L     | Н     | Driv. Add  | Invalid    |           |

| Drive Address    | F              |          | L     | Н    | L    | Н   | Н   | Н     | L     | Х          | Not Used   |           |

|                  |                | Write    | L     | L    | Н    | Н   | Н   | Н     | L     | Not used   | Х          |           |

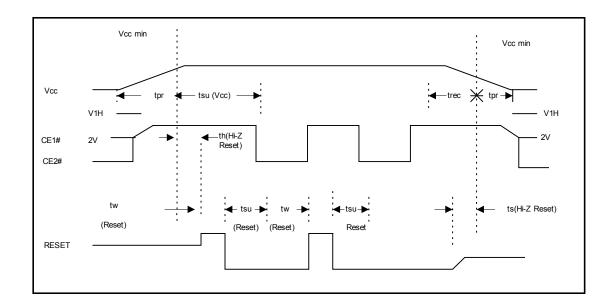

## **Table 4 PCMCIA Mode Power-On and Reset Timing Parameters**

| Symbol      | Parameter                           | Min   | Max | Units |

|-------------|-------------------------------------|-------|-----|-------|

| tsu (Vcc)   | CE# setup time from Vcc             | 20    |     | ms    |

| tsu (RESET) | CE# setup time from reset           | 20    |     | ms    |

| trec (VCC)  | CE# recovery time                   | 0.001 |     | ms    |

| tp          | Vcc rise time [10% to 0.9 (Vcc+5%]  | 0.1   | 300 | ms    |

| tp0         | Vcc fall time [0.9 (Vcc-5%) to 10%] | 3.0   | 300 | ms    |

| tw (Reset)  | Reset pulse width                   | 10    |     | ms    |

| th (Reset)  | Reset high from Vcc min             | 1     |     | ms    |

| ts (Reset)  | Reset high-z from Vcc min           | 0     |     | ms    |

#### Note

I tpr and tpf are linear waveforms' during the 10% to 90% (or vice-versa) period Even if the waveform is not a linear waveform, its rise and fall times must meet this specification.

### **Table 5 Attribute-Mode Timing Parameters**

| Symbol | IEEE    | Parameter                             | Min | Max | Units |

|--------|---------|---------------------------------------|-----|-----|-------|

| READ   |         |                                       |     |     |       |

| t1     | tAVAVR  | Read cycle time                       | 300 |     | ns    |

| t2     | tAVQV   | Address access time                   |     | 300 | ns    |

| t3     | tELQV   | Card Enable access time               |     | 300 | ns    |

| t4     | tGLQNZ  | Output Enable to data change          | 5   |     | ns    |

| t5     | tGLQV   | Output Enable access time             |     | 150 | ns    |

| t6     | tGLWtV  | Wait Valid from Output Enable         |     | 35  | ns    |

| t7     | tWtLWtH | Wait pulse width                      |     | 12  | ns    |

| t8     | tQVWtH  | Data setup for Wait released          | 0   |     | ns    |

| t9     | tAXQX   | Data valid after address change       | 0   |     | ns    |

| t10    | tGHEH   | Card Enable hold time                 | 20  |     | ns    |

| t11    | tEHQZ   | Data disable from Card Enable high    |     | 100 | ns    |

| t12    | tGHQZ   | Data disable from Output Enable high  |     | 100 | ns    |

| WRITE  |         |                                       | ·   |     |       |

| t0     | tAVAVW  | Write cycle time                      | 250 |     | ns    |

| t13    | tAVWH   | Address valid to Write Enable high    | 180 |     | ns    |

| t14    | tELWH   | Card Enable to Write Enable high      | 180 |     | ns    |

| t15    | tWLWH   | Write Enable pulse width high         | 150 |     | ns    |

| t16    | tDVWH   | Data valid to Write Enable high       | 80  |     | ns    |

| t17    | tAVWL   | Address, valid to Write Enable low    | 30  |     | ns    |

| t18    | tELWL   | Card Enable setup to Write Enable low | 0   |     | ns    |

| t19    | tWLQZ   | Write Enable to previous              |     | 100 | ns    |

| t20    | tWHDX   |                                       | 30  |     | ns    |

| t21    | tWHQNZ  |                                       | 5   |     | ns    |

| t22    | tWHAX   |                                       | 30  |     | ns    |

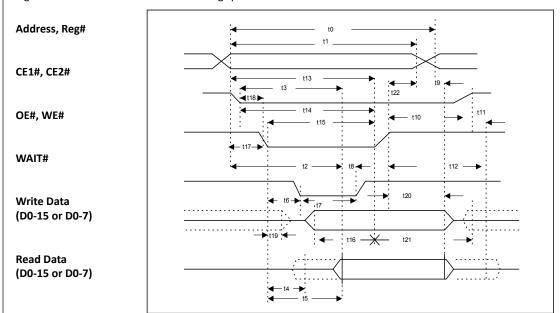

### **Attribute-Mode Timing**

Attribute memory's access time is 300ns at standard Vcc=3.3V/5V ±5% operating voltage.

Figure 6 and Table 14 show detailed timing specifications.

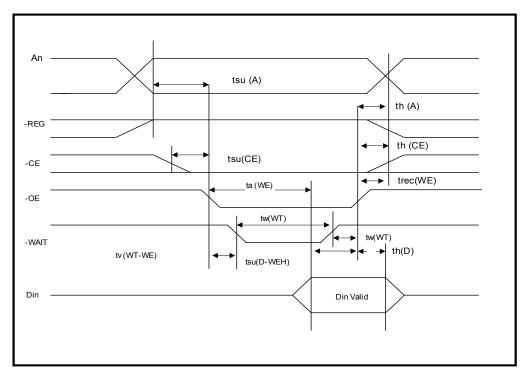

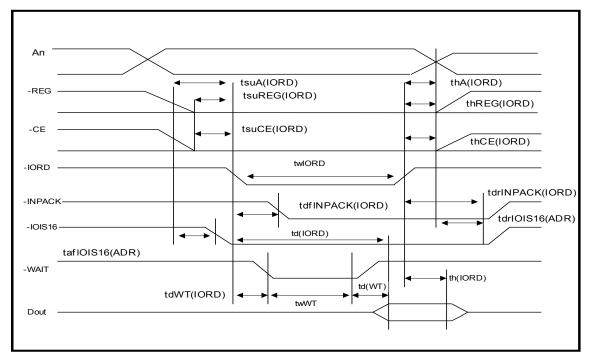

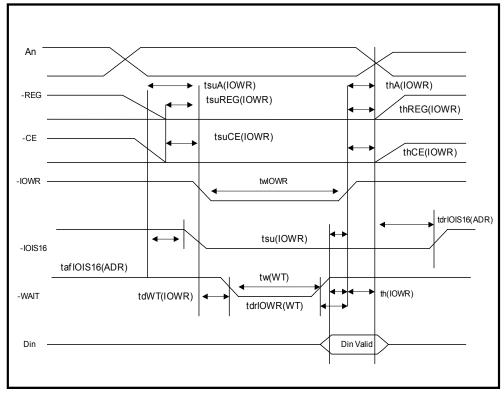

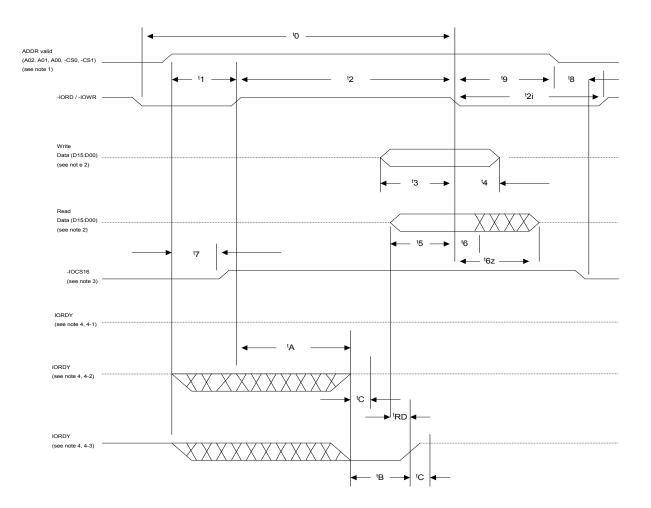

### **Interface Bus Timing**

Several bus timing must be considered when using the flash drive in PCMCIA modes: reset, attribute (or CIS-tuple), common-memory, and I/O timing.

### **PCMCIA Reset Timing**

The flash drive requires some initialization time after a power-on or hardware reset. This time is specified below.

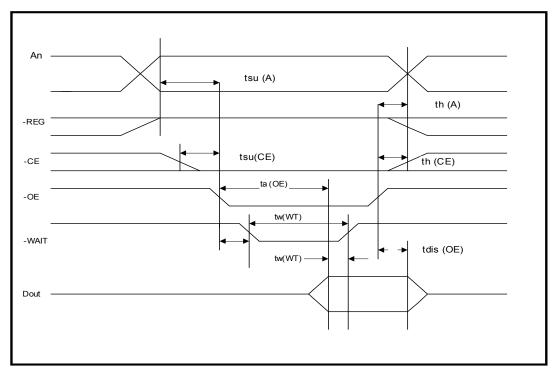

### **Common Memory Read Timing**

| Item                            | Symbol    | IEEE Symbol | Min ns. | Max ns. |

|---------------------------------|-----------|-------------|---------|---------|

| Output Enable Access Time       | ta(OE)    | tGLQV       |         | 125     |

| Output Disable Time from OE     | tdis(OE)  | tGHQZ       |         | 100     |

| Address Setup Time              | tsu(OE)   | tAVGL       | 30      |         |

| Address Hold Time               | th(A)     | tGHAX       | 30      |         |

| CE Setup before OE              | tsu(CE)   | tELGL       | 0       |         |

| CE Hold following OE            | th(CE)    | tGHEH       | 20      |         |

| Wait Delay Falling from OE      | tv(WT-OE) | tGLWTV      |         | 35      |